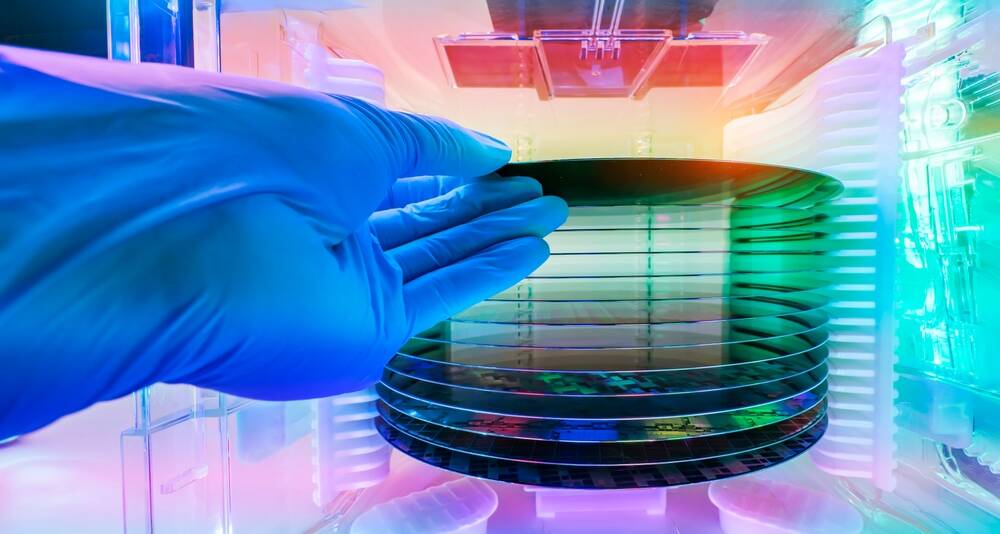

So they found a way to inscribe more arcane runes onto the mystic rock thus increasing its mana capacity?

Can’t wait for Python on top of webassembly on top of react on top of electron Frameworks to void that advancement

The more efficient the machines, the less efficient the code, such is the way od life

I’m wondering how much further size reductions in lithography technology can take us before we need to find new exotic materials or radically different CPU concepts.

Aren’t these sizes a marketing gimmick anyway? They used to mean the gate size of a transistor, but I don’t think that’s been the case for a few years now.

They’re generally consistent within a single manufacturer’s product lines; however, you absolutely cannot compare them between manufacturers because the definitions are completely different.

No, it still means what it always has, and each step still introduces good gains.

It’s just that each step is getting smaller and MUCH more difficult and we still aren’t entirely sure what to do after we get to 1. In the past we were able to go from 65nm in 2006 to 45 in 2008. We had 7nm in 2020, but in that same 2 year time frame we are only able to get to 5nm

And now we’ve reached the need for decimal steps with this 1.6.

Later each new generation process became known as a technology node[17] or process node,[18][19] designated by the process’ minimum feature size in nanometers (or historically micrometers) of the process’s transistor gate length, such as the “90 nm process”. However, this has not been the case since 1994,[20] and the number of nanometers used to name process nodes (see the International Technology Roadmap for Semiconductors) has become more of a marketing term that has no standardized relation with functional feature sizes or with transistor density (number of transistors per unit area).[21]

https://en.wikipedia.org/wiki/Semiconductor_device_fabrication#Feature_size

personally, I don’t care they try to simplify these extremely complicated chip layouts, but keep calling it X nanometers when there’s nothing of that feature size is just plain misleading.

yes, boss, I have always worked 42 hours per week… Huh? No, what do you mean “actual hours”?